Questa® CDC 解决方案仅使用 RTL(和 SDC 约束或 UPF 功耗意图文件),便可自动生成和分析断言,防止出现芯片终止跨时钟域 (CDC) 问题。可以将亚稳态模型导出到Questa Simulation进行进一步的分析,然后将所有结果通过 UCDB 传输到主验证进度数据库。不需要任何形式或属性规范语言知识。

多个时钟域带来的高风险

设计人员越来越多地使用先进的多时钟架构来满足其芯片的高性能和低功耗要求。具有多个时钟域的设计的 RTL 或门级仿真无法准确地建模与异步时钟域之间的数据传输相关的硅片行为。这导致仿真无法准确地预测硅片功能,从而产生重大错误逃逸的风险。

详尽且易于使用的自动化 CDC 验证

Questa® CDC 使用结构化分析,通过统一功耗格式 (UPF)

识别时钟域、同步器和低功耗结构,进而确定错误。它会生成用于协议验证的断言以及用于重新收敛验证的亚稳态模型。所有属性和设计意图均由软件推断。该技术详尽地检查所有潜在的

CDC 故障,以静态方式验证所有跨越异步时钟域边界的信号均受到了 CDC 同步器的保护。然后使用熟悉的原理图和波形显示描述发现的 DUT

问题。此外,CDC-FX 应用程序还与 Questa Simulation 配合,将亚稳态注入 RTL 功能仿真,以验证 DUT

能否耐受亚稳态导致的随机延迟。

业界领先的可扩展性和结果质量

在分析十亿个门的设计时,实现 “噪声” 最小化至关重要;即 CDC 分析能检测到多少个问题,这些问题是真实问题还是误报。Questa CDC

基于形式的全面、层次化分析会搜索全部DUT元素以实现高吞吐量和噪声最小化,同时提供业界领先的可扩展性和高质量的结果,并实现 CDC IP复用。

功能:

化解 CDC 验证挑战的自动化解决方案

■ 结构化验证

■ 协议验证(包括用于仿真和形式的断言)

■ 重新收敛验证

轻松设置

■ 自动化 SDC 导入和调试

■ Liberty 模型支持

■ 直接导入经 Questa Simulation 编译的库

■ Xilinx 和 Altera FPGA 库支持

新手和专家均可轻松使用

■ 自动推断时钟分组

■ 自动识别 CDC 同步结构

■ 识别 50 多种同步样式

■ 支持用于专有同步样式的自定义同步器

在每一步衡量进度指标

■ 有关所有 CDC 路径以及时钟和复位树的结构化报告

■ 所有 CDC 协议断言的覆盖率

■ 所有用于仿真的 CDC-FX 亚稳态模型的覆盖率

轻松的结果分析和调试

■ 豁免管理流程支持在整个设计流程中跟踪违规和豁免

■ 强大的 TCL API 可将 CDC 数据集中到自定义报告中

■ Questa 验证管理器集成可自动生成测试计划和趋势报告

功耗分析 CDC 验证支持

■ 支持 UPF 2.0 和 2.1

■ 考虑所有隔离和保留单元

■ 通过动态电压和频率调整 (DVFS) 分析电源域

■ 验证跨电压域 (VDC)

优势和亮点

即时生产率——Questa CDC 会自动识别您的时钟和时钟分配策略,从而最大限度缩短建立时间。只需读入您的 RTL 设计,Questa CDC 就能查明所有潜在的 CDC 问题并给出如何解决问题的建议,而无需任何测试平台。

自动修复指南——Questa CDC 会自动识别 CDC 同步结构,从附带的 50 多种同步样式中做出选择。用户还可以创建并纳入用于专有同步样式的自定义同步器。

易于设置和使用——Questa CDC 支持用于时钟和端口域设置的综合设计约束 (SDC) 格式,并且包括了具有强大控制和报告功能的 TCL 脚本环境。时钟分组是自动推断和报告的。

低噪声,高精度——Questa CDC 产生的误报数量在业内是最少的,因此用户不必浪费时间追究不是问题的问题。

低功耗意图意识——Questa CDC 接受无修改的 UPF 文件,以确保低功耗电路不会引入与 CDC 相关的问题。具体来说,Questa CDC 会考虑所有隔离和保留单元、具有动态电压和频率调整 (DVFS) 的电源域,并验证跨电压域 (VDC) 路径。

熟悉的可视化——以 CDC 为中心的分析和调试 GUI 使用与 HDL 和 UPF 关联且采用颜色编码的熟悉原理图和波形。

SoC 级别的可扩展性——Questa CDC 的高性能分析可以处理十亿个门级别的设计,其层次化方法可实现无限容量。

高性能分析——对 Questa CDC 技术的应用研究和工程进行的专门投资,实现了时钟性能、内存使用和存储消耗方面的持续改进。这意味着 Questa CDC 经常超越严苛的可扩展性和计算资源预期。

与 Questa Simulation 直接集成——已获专利的自动亚稳态注入是发现复杂的 CDC 重新收敛错误的唯一方法。验证管理——凭借用于静态 CDC 分析、协议分析和重新收敛验证(通过 UCDB)的自动测试计划生成和覆盖率报告,您可以度量 CDC 验证进度以及与 CDC 协议有关的测试平台的质量,从而有效地管理总体验证过程。

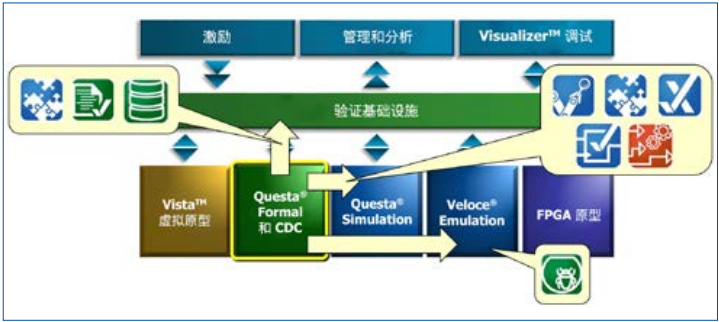

企业验证平台的一部分

企业验证平台基于多种强大的技术构建而成,并与Veloce® 硬件加速仿真紧密集成,可转换验证,显著提高生产率和更高效地管理资源。Questa CDC 和 Formal 解决方案与仿真和硬件加速仿真相集成,共享通用功能,例如验证管理、编译器、调试器以及对SystemVerilog、Verilog、VHDL、UPF 等的语言支持。这使用户可以选择适合其作业的最佳应用程序或工具,然后结合所有引擎的结果来动态跟踪整个验证计划的进度。